# nascom

# Nascom 2 Microcomputer DOCUMENTATION

The Nascom Microcomputers Division of Lucas Logic Limited reserves the right to amend/delete any specification in this brochure in accordance with future developments.

Nascom Microcomputers

Division of Lucas Logic Limited

Welton Road Wedgnock Industrial Estate

Warwick CV34 5PZ

Tel: 0926 497733 Telex: 312333

Lucas Logic

This document is the property of Nascom Microcomputers Ltd., and may not be copied, used or disclosed for any purpose except as authorised in writing by Nascom Microcomputers Ltd.

| ISSUE       | DATE        | REVISED SHEETS                                                                | REMARKS                                       |

|-------------|-------------|-------------------------------------------------------------------------------|-----------------------------------------------|

| 1.          | 18.9.78.    | (i) - (ii), 1-1,2-1,<br>3-1-3.3, 4-1, 5-1,<br>A. 1-A.2, B.2-B.2,<br>C. 1-C.2. | First formal issu                             |

| 2.          | 11.1.79     | (i)-(ii), 2.1,3.1-3.3,<br>4.1, 5.1, C.2.                                      | Revision of detai                             |

| 3.          | 18.10.79    | (i)-(ii), 1-5, App. A-C                                                       | Revised for<br>compatibility wit<br>NASCOM 2. |

|             |             |                                                                               |                                               |

|             |             |                                                                               |                                               |

|             |             |                                                                               |                                               |

|             |             |                                                                               |                                               |

|             |             |                                                                               |                                               |

| ORIGINATOR: | D.R. WADHAM | APPROVAL: Dave                                                                | Lewis                                         |

#### CONTENTS

- 1. Introduction

- 2. References

- 3. Functional Description

- 4. Electrical Specification

- 4.1 Tristate Logic

- 4.2 Open Collector

- 4.3 Power Supplies

- 4.4 General Design Points

- 5. Physical Specification

- 5.1 Board Specification

- 5.1.1 Board Dimensions

- 5.1.2 Contact Pitch

- 5.2 Connector Specification

- 5.3 Mother Board Specification

- 5.3.1 Board Dimensions

- 5.3.2 Linking

## Appendices

Appendix A - Board Outline

Appendix B - Connector Outline

Appendix C - NASBUS Summary

## 1. Introduction

The NASBUS is a bus used to add extra boards (e.g. memory and I/O) to the basic NASCOM Microcomputer. It consists mainly of buffered Z8O input and output signals together with some additional bus control lines.

The equipment practice used has been chosen for its wide availability and low cost.

This document defines the electrical and physical characteristics of the NASBUS.

#### 2. References

This specification should be read in conjunction with the following documents:

- 1. Z80 Microcomputer devices Technical Manual MK 3880 Central Processing Unit Mostek.

- VERO catalogue.

- Mostek Z80 Technical Manual

MK 3881 Parallel I/O Controller

#### 3. Functional Description

The Nasbus is a 77 way bus, with signals allocated as described below. Please see the  $280\ CPU$  manual (1) for details of timing and operation of  $280\ derived$  signals.

Note that lines marked "Reserved" have already been allocated for future use.

| PIN      | SIGNAL NAME        | DESCRIPTION                                                                                                                                                                                                                                                                               |

|----------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1        | Ov                 | •                                                                                                                                                                                                                                                                                         |

| 2        | Ov                 | Power supply and system ground                                                                                                                                                                                                                                                            |

| 3        | 0v                 | rower suppry and system growing                                                                                                                                                                                                                                                           |

| 4<br>5   | Ov<br>Clock        | Buffered system clock 1/2 MHz for Nascom 1.                                                                                                                                                                                                                                               |

| J        | CIOCK              | 2/4 MHz for Nascom 2.                                                                                                                                                                                                                                                                     |

| 6        | NMI SWITCH *       | An active low signal which initiates a short pulse on the Z80 CPU NMI pin (but not necessarily on bus line 21). Nascom 2 provides this facility.                                                                                                                                          |

| 7        | (reserved)         | F                                                                                                                                                                                                                                                                                         |

| 8        | (reserved)         |                                                                                                                                                                                                                                                                                           |

| 9        | RAM DISABLE*       | An active low signal which disables output from any RAM on the bus. Used to give ROM priority over RAM.                                                                                                                                                                                   |

| 10       | RESET SWITCH *     | An active low signal which initiates a short                                                                                                                                                                                                                                              |

|          |                    | pulse on the RESET line (pin 14), to reset<br>the system without destroying dynamic RAM<br>contents.                                                                                                                                                                                      |

| 11       | NASCOM MEM         | A decoded signal from one of the RAM boards in                                                                                                                                                                                                                                            |

|          |                    | the system defining which 4K memory block is used by the NASCOM 1. (Usually 0000H - 0FFFH).                                                                                                                                                                                               |

| 12       | NASCOM IO          | Not used by NASCOM 2.  A decoded signal from an IO expansion card                                                                                                                                                                                                                         |

| 13       | DBDR *             | defining which ports are used on the NASCOM.                                                                                                                                                                                                                                              |

| 13       | DBDR "             | This signal 'Data bus drive' determines the direction of the bidirectional data bus                                                                                                                                                                                                       |

|          |                    | buffers on the NASCOM Buffer card. It is a decoded signal made active by any device transferring data to the NASCOM card. Active low to drive data to the NASCOM. (Although this signal is not used by NASCOM 2 it must be generated by any peripheral card to ensure                     |

| 14       | RESET *            | operation with a buffered NASCOM 1). The main system reset line. The duration of of the RESET pulse is restricted to about 7 uS. to maintain dynamic RAM refresh. The line is unbuffered and bidirectional, 1.e. the RESET signal may be either generated or used by any card in the bus. |

| 15       | HALT               | Buffered Z8O HALT signal.                                                                                                                                                                                                                                                                 |

| 16       | BAI * * or TEST *  | These signals are used to provide a 'daisy                                                                                                                                                                                                                                                |

| 17       | BAO * *            | chain' Bus acknowledge signal for priority                                                                                                                                                                                                                                                |

|          |                    | bus control during DMA. On the NASCOM 2 CPU card line 16 (normally BAI) is used for an active low TEST facility which floats the address and most control signal buffers. As usual for a CPU card, line 17(BAO) = buffered CPU BUSAK signal.                                              |

| 18       | BUSRQ *            | Z80 BUSRQ signal. Used by external devices to<br>request control of the data, address and control                                                                                                                                                                                         |

| 10       |                    | lines.                                                                                                                                                                                                                                                                                    |

| 19<br>20 | IEI * *<br>IEO * * | These signals form a 'daisy chain' connection for interrupt priority control.                                                                                                                                                                                                             |

| 21       | NMI *              | On the NASCOM 1 the Z80 Non Maskable Interrupt is                                                                                                                                                                                                                                         |

|          |                    | dedicated to the monitor single step feature. This line is reserved for NMI for users who require to generate this signal on the bus and is accepted as a buffered input by the NASCOM 2.                                                                                                 |

| 22       | ĪNT *              | Z80 interrupt request line.                                                                                                                                                                                                                                                               |

| 23       | WAIT *             | Z80 WAIT line                                                                                                                                                                                                                                                                             |

|          |                    | •                                                                                                                                                                                                                                                                                         |

Page 3 Issue 3

```

SIGNAL NAME

DESCRIPTION

PIN

RFSH

Tristate buffered Z80 RFSH signal

24

\overline{\mathtt{Ml}}

Tristate buffered 280 Ml

25

26

IORO

Tristate buffered Z80 TORQ

Tristate buffered Z80 MREQ

27

MREQ

Tristate buffered 280 \overline{\text{WR}}

\overline{\mathtt{WR}}

28

Tristate buffered 280 RD

RD

29

30

ΑO

32

A3

34

35

A4

Α5

36

37

A6

Α7

38

39

Α8

Tristate 280 Address lines 0 to 15

Α9

40

Alo

41

All

A12

A13

42

43

44

A14

45

A15

46

47

Reserved

48

49

50

DO

51

DI

52

D2

53

D3

54

55

D4

Bidirectional, Tristate Z80 Data lines

D5

0 to 7.

56

D6

57

D7

59

60

61

Reserved

62

63

64

65

66

Unused (to provide separation of signal and power lines).

67

-5V

-5V

68

Power supply

69

70

-12V

71

72

-12v

Keyway

73

74

+12Ÿ

Power supply

+12V

75

+ 5V

76

77

+ 5V

+ 5V

78

+ 5V

```

Designers should recognise that the frequency of the system clock may change at some future date (as a result of system upgrades/improvements) and should allow for this possibility.

<sup>\* = &</sup>quot;Open Collector" signal line

<sup>\*\*</sup> note (i) link on any card not using these (IEI - IEO and/or BAI - BAO).

(ii) bus tracks must be broken near any card socket using these

lines

(iii) buffer card and NASCOM 2 provide a pull up resistor for IEO

Issue 3

#### Electrical Specification 4.

#### 4.1 Tristate Logic

These lines are driven by low power Schottky tristate buffers capable of sinking 16 mA-i.e. capable of driving 10 standard TTL loads (1.6mA sinking, 40 u A source) or approximately 40 low power Schottky inputs (0.36 mA sinking, 20 u A source) while retaining logic zero <0.4v and logic 1>2.4v.

#### 4,2 Open Collector

Open collector lines are pulled up to 5 v. Any, board can pull down to zero provided it is capable of sinking  $16\ \text{mA}$ .

#### 4.3 Power supplies

In order to avoid overloading the motherboard and the system power supplies the following rules should be applied.

- (a) All bus lines of the same voltage should be commoned on any plug-in board.

- (b) No board should draw a total of more than:

- + 5v 2.0 Amps 5v 0.5 Amp + 12v 1.0 Amp 12v 0.5 Amp

- (c) The whole occupied Nasbus should not draw more than:

- + 5v 8 Amps

- 5v 1 Amp

- + 12v 2 Amps

- 12 v 1 Amp

#### 4.4 General Design Points

Boards should be designed where possible to apply no more than 2 or 3 low power loads to any signal line of the Nasbus. In any event, a maximum of 1 TTL load must not be exceeded.

Capacitance limits of 40pF for Data bus lines and 20pF for all others are advised.

The above figures may be somewhat exceeded on a CPU card.

RD, WR, MREQ, TORQ, MI, RESH should be pulled up to +5v with a 10K resistor where feasible.

Note that tristate lines will float if the Nascom CPU is disabled e.g. by a bus request.

No board may be plugged into or removed from the bus when power supplies are live. It is advisable to wait for up to 2 minutes after switching supplies "off".

Issue 3

#### Physical Specification

#### 5.1 Board Specification

#### 5.1.1 Board Dimensions

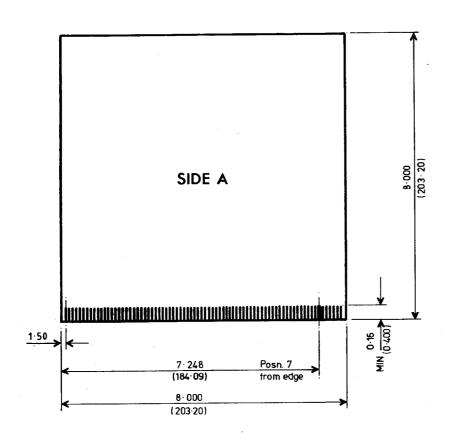

The standard board size is 203.20mm long + 0.00, - 0.30 by 203.20mm. high + 0.00, - 0.25 (i.e. 8 x 8 inches). The thickness should be 1.60 nominal (including copper). See also Appendix A.

A suitable prototyping board is Vero type 10-0155 F (up to 45 DIPs) Type Nos. 06-3462C and 06-3463J can also be used.

#### 5.1.2 Contact Pitch

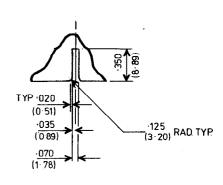

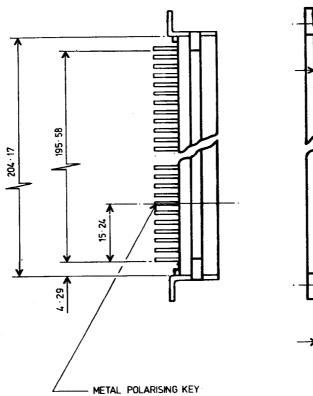

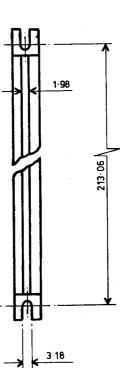

The contact pitch 1s 2.54mm. 77 of the possible 78 ways are used, with a reference key 7 from the bottom. The contacts used are on the solder side, and it is recommended that they are hard gold plated.

#### 5.2 Connector Specification

Suitable connectors are Vero type 14-0998G (with polarising key in position 72) or Varelco type 00.6072-080-657-101 with polarising key at position 73, positions 1 and 80 blank. (See Appendix B).

#### 5.3 Mother Board Specification

#### Board Material

The preferred material is GlO or FR4 epoxy glass (because of the mechanical strains involved). However, a section of SRBP 78 way Veroboard type 67-1902F (about  $15\frac{1}{2}$ " x 8") may be used with care.

#### 5.3.2 Linking

Appropriate power supply lines should be commoned together by links on the Mother Board.

To reduce both AC Impedance and DC resistance of the two main supply rails it is advisable to add one length of, say, 22 SWG tinned copper wire behind the top 4 lines (Nos. 1-4: OV.) and another behind the bottom 4 lines (Nos.75-78: +5v). These wires are easily fitted if the relevant 4 pins of each connector are bent together and the horizontal bus wires wound round them before soldering.

Lines 16 and 17, and 19 and 20 should be cut and linked between sockets to provide daisy chain Bus Acknowledge and Interrupt Enable signals (see section 3 and reference 3).

APPENDIX A

BOARD OUTLINE

Detail of Polarising Key

APPENDIX B

CONNECTOR OUTLINE

# APPENDIX C

# NASBUS SUMMARY

Lines marked \* are open collector: those overlined are  $\overline{\text{NOT}}$  (logic level).

| 1,2,3,4        | OV: GROUND                         |

|----------------|------------------------------------|

| 5              | Ø (buffered clock)                 |

| 6              | NMI SWITCH *                       |

|                | reserved                           |

| 7,8            |                                    |

| 9              | RAMDISABLE*                        |

| 10             | RESET SWITCH *                     |

| 11             | NASCOM MEM                         |

| 12             | NASCOM IO                          |

| 13             | DBDR*                              |

|                | RESET*                             |

| 14             |                                    |

| 15             | HALT                               |

| 16             | BAI (or TEST* for CPU card)        |

| 17             | BAO                                |

| 18             | BUSRQ*                             |

| 19             | IEI                                |

|                | IEO                                |

| 20             |                                    |

| 21             | NMI*                               |

| 22             | INT*                               |

| 23             | WAIT*                              |

| 24             | RESH                               |

| 25             | M1                                 |

|                |                                    |

| 26             | IORQ                               |

| 27             | MREQ                               |

| 28             | <u>WR</u>                          |

| 29             | RD ·                               |

| 30             | AO                                 |

| 31             | Al                                 |

| 32             | A2                                 |

|                | A3                                 |

| 33             |                                    |

| 34             | A4                                 |

| 35             | A5_                                |

| 36             | A6                                 |

| 37             | A7                                 |

| 38             | A8                                 |

| 39             | A9                                 |

| 40             | Alo                                |

| 41             | A11                                |

|                | A12                                |

| 42             | A13                                |

| 43             |                                    |

| 44             | A14                                |

| 45             | A15                                |

| 46, 47, 48, 49 | Reserved                           |

| 50             | DO .                               |

| 51             | Dl                                 |

| 52             | D2                                 |

| 53             | D3                                 |

| 54             | D4                                 |

|                | D5                                 |

| 55             | D6                                 |

| <u>56</u>      |                                    |

| 57             | D7                                 |

| 58, 59, 60 65  | Reserved                           |

| 66, 67         | To separate signal and power lines |

| 68, 69         | -ve 5V                             |

| 70, 71         | -ve 12V                            |

| 72             | KEY                                |

| 73, 74         | +ve 12V                            |

| 75, 76, 77, 78 | tve 5V                             |

|                | · · · <del>-</del> ·               |

|                |                                    |

#### INTERRUPT AND BUS ACKNOWLEDGE DAISY CHAINS

It is necessary to assign to each board in the system a priority for use of the bus and for operation of interrupts. It is conventional to assign the same priority for each function to a given board.

Lines 16 and 17 of NASBUS provide the bus acknowledge daisy chain lines; lines 19 and 20 are used for the interrupt enable daisy chain. It is necessary for one signal of each pair to enter boards always on the same bus line, the other leaving boards on the adjacent line. Inputs (BAI and IEI) are on lines 16 and 19 respectively, outputs (BAO and IEO) being adjacent on lines 17 and 20 respectively. Clearly the use of a normal motherboard will frustrate operation of these systems, since all inputs will be common, as will the outputs. Modification of the motherboard will therefore be required in large systems to ensure correct operation of the priority systems and to permit priority selection of the boards in the computer system.

Veroboard motherboards should be modified exactly in accordance with the diagram below. NASCOM MaxiMotherboards should be wired according to the instructions supplied with them; it should be noted that they may be set up to assign priority from either end of the bus. NASCOM MiniMotherboards are already wired for priority and assign it automatically.

Care should be taken in the construction of unusual systems, particularly those in which the bus is driven unconventionally, to ensure that line 16 is always driven by line 17 and that line 19 is always driven by line 20.

In the conventional arrangement the board furthest from the CPU board's point of access to the bus is assigned the highest priority; this does not imply that the motherboard slot at the far end of the bus need necessarily be used; it is desirable to expand the bus from the processor end, moving all boards along as necessary to preserve the priority structure. This technique will reduce the propagation effects of an extended bus as far as is possible.

|    | Ø |   | 1 |   | 2   |   | 3 |     | 4 |

|----|---|---|---|---|-----|---|---|-----|---|

| 15 | • | 0 | • | 0 | •   | 0 |   | 0   | • |

| 16 |   | • | • | • | •   | • |   | •   | • |

| 17 | • |   | • | - | •   |   |   |     | • |

| 18 |   | 0 | • | 0 | •   | 0 | • | 0   | • |

| 19 |   | • | • | • | • ] | 1 | • |     | • |

| 20 |   |   | • |   | •   | • |   |     |   |

| 21 | • | 0 | • | 0 | •   | 0 | • | O . | • |

|    |   | • |   |   |     | · |   |     |   |

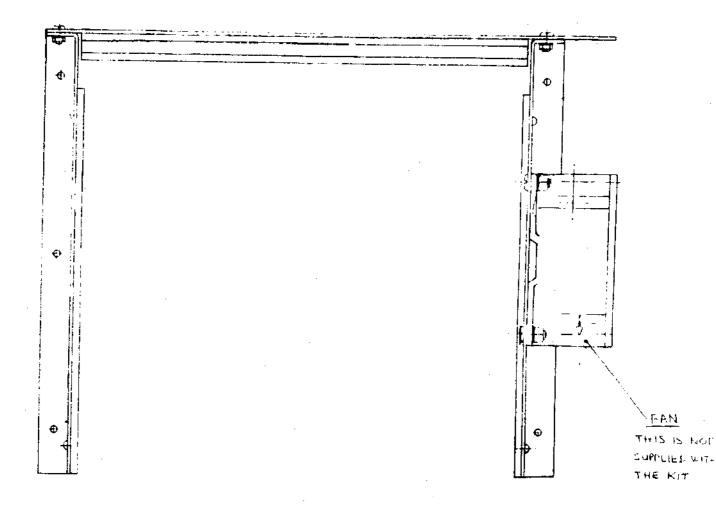

#### NASCOM FRAME KIT

Lucas Logic Limited Welton Road Wedgnock Industrial Estate Warwick CV34 5PZ

Telephone: Warwick (0926) 497733

Telex: 312333

Parts List

| Qty | Item                     |

|-----|--------------------------|

| 1   | Left Side Panel          |

| 1   | Right Side Panel         |

| 1   | Backplane board          |

| 8   | Card guides              |

| 4   | M3 screws                |

| 4   | M3 star washers          |

| 4   | M3 nuts                  |

| 4   | No 6 self tapping screws |

| 5   | Terminal pins            |

# Instructions (refer to drawing)

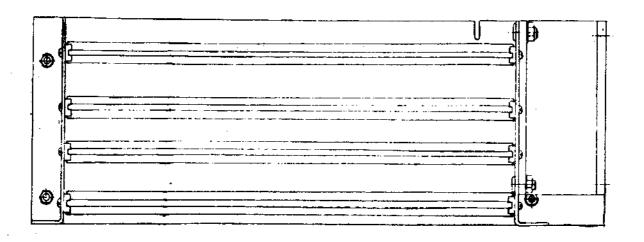

- 1) Solder the terminal pins to the 5 power supply points on the backplane board

- 2) Solder the 77 way edge connectors from your Nascom Kits to the backplane mounting them with the contacts towards the bottom of the board.

- 3) Solder a sleeved wire link from SK2 pin B71 to SK3 pin B71 (-12v rail).

- 4) Solder a sleeved wire link from SK2 pin B73 to SK3 pin B73 (+12v rail).

- 5) Solder a sleeved wire link from SK2 pin B76 to SK3 pin B76 (+5v rail).

- 6) Fit the card guides to each side panel.

- 7) It is recommended that a fan is fitted on the left side panel if more than one Nascom board is to be used in the Nascom case.

- 8) Assemble the side panel to the backplane with the screws, star washers and nuts provided.

- 9) Self tapping screws are provided to mount the Nascom frame in the Nascom case.